### Intel® 965 Express Chipset Family

#### **Datasheet**

- For the Intel® 82Q965, 82Q963, 82G965 Graphics and Memory Controller Hub (GMCH) and Intel® 82P965 Memory Controller Hub (MCH)

July 2006

Document Number: 313053-002

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel® 82P965 Memory Controller Hub (MCH) and the Intel® 82Q965, 82Q963, 82G965 Graphics and Memory Controller Hub (GMCH) may contain design defects or errors known as errata, which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Hyper-Threading Technology requires a computer system with an Intel® Pentium® processor supporting Hyper-Threading Technology and an HT Technology enabled chipset, BIOS, and an operating system. Performance will vary depending on the specific hardware and software you use. See <a href="http://www.intel.com/info/hyperthreading">http://www.intel.com/info/hyperthreading</a> for information including details on which processors support HT Technology.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Intel® Active Management Technology requires the platform to have an Intel® AMT-enabled chipset, network hardware and software. The platform must also be connected to a power source and an active LAN port. See Intel® Active Management Technology for additional information.

$I^2C$  is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the  $I^2C$  bus/protocol and was developed by Intel. Implementations of the  $I^2C$  bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Intel, Pentium, Intel Core, Core Inside, and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright<sup>©</sup> 2006, Intel Corporation

### **Contents**

| 1 | Introd               | luction                                                                             | 19        |  |  |  |

|---|----------------------|-------------------------------------------------------------------------------------|-----------|--|--|--|

|   | 1.1                  | Terminology                                                                         | 24        |  |  |  |

|   | 1.2                  | Reference Documents                                                                 |           |  |  |  |

|   | 1.3                  | (G)MCH Overview                                                                     |           |  |  |  |

|   |                      | 1.3.1 Host Interface                                                                |           |  |  |  |

|   |                      | 1.3.2 System Memory Interface                                                       |           |  |  |  |

|   |                      | 1.3.3 Direct Media Interface (DMI)                                                  | 29        |  |  |  |

|   |                      | 1.3.4 PCI Express* Interface (Intel® 82Q965, 82G965, 82P965 (G)MCI                  | Η         |  |  |  |

|   |                      | Only)                                                                               | 29<br>965 |  |  |  |

|   |                      | 1.3.6 Alerting Standard Format (ASF) (Intel <sup>®</sup> 82Q965 and 82Q963 GM Only) | CH        |  |  |  |

|   |                      | 1.3.7 Graphics Features (Intel <sup>®</sup> 82Q965, 82Q963, 82G965 GMCH)            | 31        |  |  |  |

|   |                      | 1.3.8 SDVO and Analog Display Features (Intel® 82Q965, 82Q963, 82                   |           |  |  |  |

|   |                      | GMCH Only)                                                                          | 32        |  |  |  |

|   |                      | 1.3.9 (G)MCH Clocking                                                               | 33        |  |  |  |

|   |                      | 1.3.10 Thermal Sensor                                                               |           |  |  |  |

|   |                      | 1.3.11 Power Management                                                             | 33        |  |  |  |

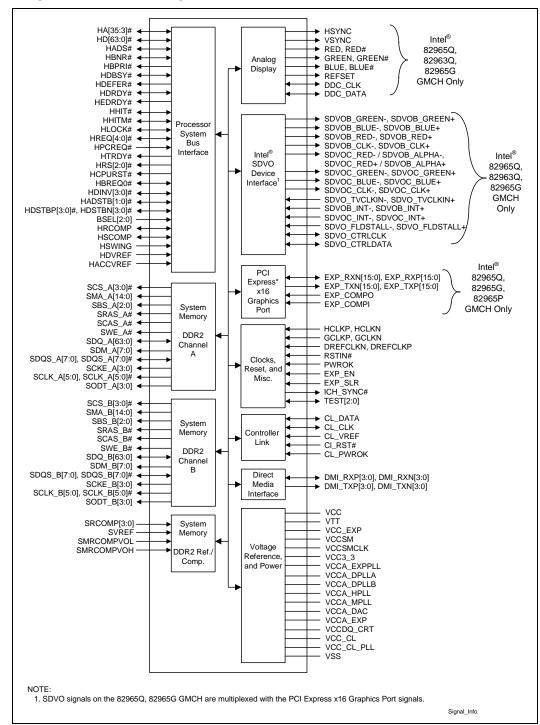

| 2 | Signal Description35 |                                                                                     |           |  |  |  |

|   | 2.1                  | Host Interface Signals                                                              |           |  |  |  |

|   | 2.2                  | DDR2 DRAM Channel A Interface                                                       | 40        |  |  |  |

|   | 2.3                  | DDR2 DRAM Channel B Interface                                                       | 41        |  |  |  |

|   | 2.4                  | DDR2 DRAM Reference and Compensation                                                | 42        |  |  |  |

|   | 2.5                  | PCI Express* Interface Signals (Intel® 82Q965, 82G965, 82P965 (G)MCH Only)          |           |  |  |  |

|   | 2.6                  | Analog Display Signals (Intel® 82Q965, 82Q963, 82G965 GMCH Only)                    | 43        |  |  |  |

|   | 2.7                  | Clocks, Reset, and Miscellaneous                                                    |           |  |  |  |

|   | 2.8                  | Direct Media Interface (DMI)                                                        |           |  |  |  |

|   | 2.9                  | Controller Link (CL)                                                                |           |  |  |  |

|   | 2.10                 | Intel® Serial DVO (SDVO) Interface (Intel® 82Q965, 82Q963, 82G965 GM                |           |  |  |  |

|   | 2.10                 | Only)                                                                               |           |  |  |  |

|   | 2.11                 | Power and Ground                                                                    |           |  |  |  |

| 3 | Systen               | m Address Map                                                                       | 49        |  |  |  |

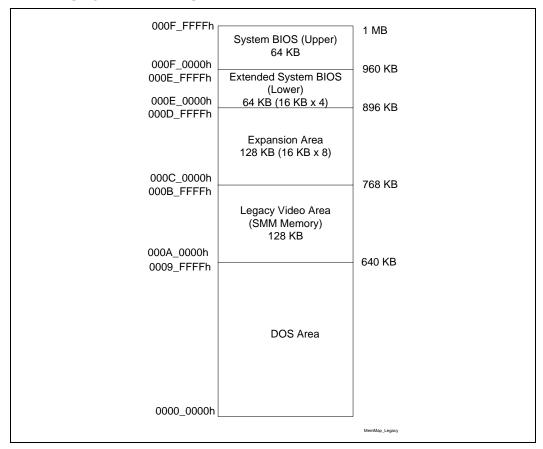

|   | 3.1                  | Legacy Address Range                                                                | 52        |  |  |  |

|   |                      | 3.1.1 DOS Range (0h – 9_FFFFh)                                                      |           |  |  |  |

|   |                      | 3.1.2 Legacy Video Area (A_0000h-B_FFFFh)                                           | 53        |  |  |  |

|   |                      | 3.1.3 Expansion Area (C_0000h-D_FFFFh)                                              |           |  |  |  |

|   |                      | 3.1.4 Extended System BIOS Area (E_0000h-E_FFFFh)                                   |           |  |  |  |

|   |                      | 3.1.5 System BIOS Area (F_0000h-F_FFFFh)                                            |           |  |  |  |

|   |                      | 3.1.6 PAM Memory Area Details                                                       |           |  |  |  |

|   | 2.2                  | 3.1.7 Legacy Interrupt Routing                                                      |           |  |  |  |

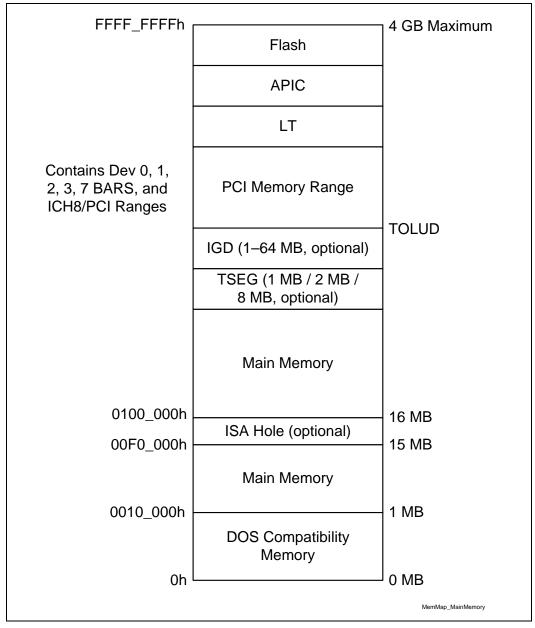

|   | 3.2                  | Main Memory Address Range (1 MB – TOLUD)                                            |           |  |  |  |

|   |                      | 3.2.1 ISA Hole (15 MB – 16 MB)                                                      | 58        |  |  |  |

|         | 3.2.2              | ISEG                                                            |           |

|---------|--------------------|-----------------------------------------------------------------|-----------|

|         | 3.2.3              | Pre-allocated Memory                                            |           |

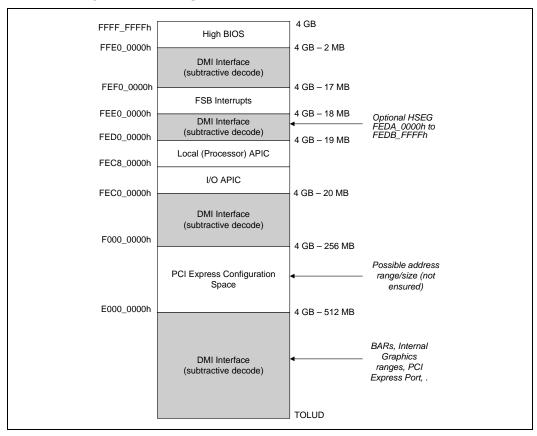

| 3.3     |                    | ory Address Range (TOLUD – 4 GB)                                |           |

|         | 3.3.1              | APIC Configuration Space (FEC0_0000h-FECF_FFFFh)                | .60       |

|         | 3.3.2              | HSEG (FEDA_0000h-FEDB_FFFFh)                                    | .60       |

|         | 3.3.3              | FSB Interrupt Memory Space (FEEO_0000-FEEF_FFFF)                | .60       |

|         | 3.3.4              | High BIOS Area                                                  | .61       |

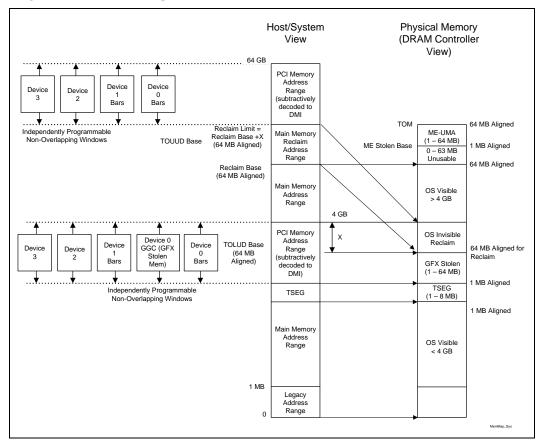

| 3.4     | Main Mer           | mory Address Space (4 GB to TOUUD)                              | .61       |

|         | 3.4.1              | Memory Re-claim Background                                      |           |

|         | 3.4.2              | Memory Reclaiming                                               | .62       |

| 3.5     | PCI Expr<br>(G)MCH | ess* Configuration Address Space (Intel® 82Q965, 82G965, 82P965 | ;<br>.62  |

| 3.6     | PCI Expr           | ess* Graphics Attach (PEG) (Intel® 82Q965, 82G965, 82P965 (G)M  | СН        |

|         | Only)              |                                                                 | .63       |

| 3.7     | , ,                | Memory Address Ranges (Intel® 82Q965, 82Q963, 82G965 GMCH       |           |

| <b></b> |                    |                                                                 | .64       |

| 3.8     |                    | Management Mode (SMM)                                           |           |

| 5.0     | 3.8.1              | SMM Space Definition                                            |           |

|         | 3.8.2              | SMM Space Restrictions                                          | .05<br>65 |

|         | 3.8.3              | SMM Space Combinations                                          |           |

|         | 3.8.4              | SMM Control Combinations                                        |           |

|         | 3.8.5              | SMM Space Decode and Transaction Handling                       |           |

|         | 3.8.6              | Processor WB Transaction to an Enabled SMM Address Space        |           |

|         | 3.8.7              | SMM Access Through GTT TLB (Intel® 82Q965, 82Q963, 82G965       |           |

|         | 51017              | GMCH Only)                                                      | .67       |

| 3.9     | Memory             | Shadowing                                                       |           |

| 3.10    | •                  | ess Space                                                       |           |

| 5.10    | 3.10.1             | PCI Express* I/O Address Mapping (Intel® 82Q965, 82G965, 82P9   |           |

|         | 3.10.1             | (G)MCH Only)                                                    |           |

| 2 11    | (C)MCH             | Decode Rules and Cross-Bridge Address Mapping                   |           |

| 3.11    |                    |                                                                 |           |

|         | 3.11.1             | Legacy VGA and I/O Range Decode Rules                           | . / 0     |

| (G)MCH  | H Register         | Description                                                     | .71       |

| 4.1     | _                  | Terminology                                                     |           |

|         |                    |                                                                 |           |

| 4.2     | _                  | ation Process and Registers                                     |           |

| 4.5     | 4.2.1              | Platform Configuration Structure                                |           |

| 4.3     |                    | ation Mechanisms                                                |           |

|         | 4.3.1              | Standard PCI Configuration Mechanism                            |           |

|         | 4.3.2              | PCI Express* Enhanced Configuration Mechanism (Intel® 82Q965,   | ٦.        |

|         |                    | 82G965, 82P965 (G)MCH Only)                                     |           |

| 4.4     |                    | Configuration Accesses                                          |           |

|         | 4.4.1              | Internal Device Configuration Accesses                          |           |

|         | 4.4.2              | Bridge Related Configuration Accesses                           |           |

| 4.5     |                    | ped Registers                                                   |           |

|         | 4.5.1              | CONFIG_ADDRESS—Configuration Address Register                   |           |

|         | 4.5.2              | CONFIG_DATA—Configuration Data Register                         | .81       |

| Hoct P  | ridae/DDA          | M Controller Registers (Device 0, Function 0)                   | ۵၁        |

|         | -                  | - , , , , , , , , , , , , , , , , , , ,                         | .03       |

| 5.1     |                    | dge/DRAM Controller Configuration Register Details (Device 0,   | _         |

|         |                    | 0)                                                              |           |

|         | 5.1.1              | VID—Vendor Identification                                       |           |

|         | 5.1.2              | DID—Device Identification                                       | .85       |

|         |                    |                                                                 |           |

| 5.1.3  | PCICMD—PCI Command                                          |      |

|--------|-------------------------------------------------------------|------|

| 5.1.4  | PCISTS—PCI Status                                           |      |

| 5.1.5  | RID—Revision Identification                                 | .88  |

| 5.1.6  | CC-Class Code                                               | .88  |

| 5.1.7  | MLT—Master Latency Timer                                    | .89  |

| 5.1.8  | HDR—Header Type                                             | .89  |

| 5.1.9  | SVID—Subsystem Vendor Identification                        |      |

| 5.1.10 | SID—Subsystem Identification                                |      |

| 5.1.11 | CAPPTR—Capabilities Pointer                                 |      |

| 5.1.12 | PXPEPBAR—PCI Express* Egress Port Base Address (Intel®      | . 50 |

| 5.1.12 | 82Q965/82G965/82P965 (G)MCH Only)                           | 01   |

| 5.1.13 | MCHBAR—(G)MCH Memory-Mapped Register Range Base             | 92   |

| 5.1.14 | GGC—GMCH Graphics Control Register (Intel® 82Q965, 82Q963,  | . 52 |

| 3.1.14 | 82G965 GMCH Only)                                           | 02   |

| 5.1.15 | DEVEN—Device Enable                                         | .93  |

| 5.1.16 | PCI EXPRESS*XBAR—PCI Express* Register Range Base Address   | . 94 |

| 5.1.16 | (Intel® 82Q965, 82G965, 82P965 (G)MCH Only)                 | 0.5  |

| 5.1.17 |                                                             |      |

|        | DMIBAR—Root Complex Register Range Base Address             |      |

| 5.1.18 | PAM0—Programmable Attribute Map 0                           |      |

| 5.1.19 | PAM1—Programmable Attribute Map 1                           | .99  |

| 5.1.20 | PAM2—Programmable Attribute Map 2                           | 100  |

| 5.1.21 | PAM3—Programmable Attribute Map 3                           | 101  |

| 5.1.22 | PAM4—Programmable Attribute Map 4                           | 102  |

| 5.1.23 | PAM5—Programmable Attribute Map 5                           |      |

| 5.1.24 | PAM6—Programmable Attribute Map 6                           |      |

| 5.1.25 | LAC—Legacy Access Control                                   |      |

| 5.1.26 | REMAPBASE—Remap Base Address Register                       |      |

| 5.1.27 | REMAPLIMIT—Remap Limit Address Register                     |      |

| 5.1.28 | SMRAM—System Management RAM Control                         |      |

| 5.1.29 | ESMRAMC—Extended System Management RAM Control              |      |

| 5.1.30 | TOM—Top of Memory                                           |      |

| 5.1.31 | TOUUD—Top of Upper Usable DRAM                              | 111  |

| 5.1.32 | GBSM—Graphics Base of Stolen Memory (Intel® 82G965, 82Q965, |      |

|        | 82063Q GMCH Only)                                           |      |

| 5.1.33 | TSEGMB—TSEG Memory Base                                     |      |

| 5.1.34 | TOLUD—Top of Low Usable DRAM                                |      |

| 5.1.35 | ERRSTS—Error Status                                         |      |

| 5.1.36 | ERRCMD—Error Command                                        |      |

| 5.1.37 | SMICMD—SMI Command                                          |      |

| 5.1.38 | SKPD—Scratchpad Data                                        |      |

| 5.1.39 | CAPIDO—Capability Identifier                                |      |

| MCHBAR | Registers                                                   | 118  |

| 5.2.1  | CHDECMISC—Channel Decode Miscellaneous                      | 121  |

| 5.2.2  | CODRBO—Channel O DRAM Rank Boundary Address O               | 122  |

| 5.2.3  | CODRB1—Channel O DRAM Rank Boundary Address 1               | 123  |

| 5.2.4  | CODRB2—Channel O DRAM Rank Boundary Address 2               | 124  |

| 5.2.5  | CODRB3—Channel O DRAM Rank Boundary Address 3               |      |

| 5.2.6  | CODRA01—Channel 0 DRAM Rank 0,1 Attribute                   | 125  |

| 5.2.7  | CODRA23—Channel O DRAM Rank 2,3 Attribute                   |      |

| 5.2.8  | COCYCTRKPCHG—Channel 0 CYCTRK Precharge                     |      |

| 5.2.9  | COCYCTRKACT—Channel 0 CYCTRK ACT                            |      |

| 5.2.10 | COCYCTRKWR—Channel 0 CYCTRK WR                              |      |

| 5.2.11 | COCYCTRKRD—Channel 0 CYCTRK READ                            |      |

| 5.2.12 | COCYCTRKREFR—Channel 0 CYCTRK REFR                          |      |

| 5.2.13 | COCKECTRL—Channel 0 CKE Control                             |      |

|        |                                                             |      |

5.2

|   |         | 5.2.14<br>5.2.15<br>5.2.16 | COREFRCTRL—Channel 0 DRAM Refresh Control                            |

|---|---------|----------------------------|----------------------------------------------------------------------|

|   |         | 5.2.17                     | C1DRB1—Channel 1 DRAM Rank Boundary Address 1                        |

|   |         | 5.2.18                     | C1DRB2—Channel 1 DRAM Rank Boundary Address 2                        |

|   |         | 5.2.19                     | C1DRB43—Channel 1 DRAM Rank Boundary Address 3                       |

|   |         | 5.2.20                     | C1DRA01—Channel 1 DRAM Rank 0,1 Attributes                           |

|   |         | 5.2.21                     | C1DRA23—Channel 1 DRAM Rank 2,3 Attributes                           |

|   |         | 5.2.22                     | C1CYCTRKPCHG—Channel 1 CYCTRK PreCharge                              |

|   |         | 5.2.23                     | C1CYCTRKACT—Channel 1 CYCTRK ACT                                     |

|   |         | 5.2.24                     | C1CYCTRKWR—Channel 1 CYCTRK Write                                    |

|   |         | 5.2.25                     | C1CYCTRKRD—Channel 1 CYCTRK Read                                     |

|   |         | 5.2.26                     | C1CKECTRL—Channel 1 CKE Control                                      |

|   |         | 5.2.27                     | C1REFRCTRL—Channel 1 DRAM Refresh Control                            |

|   |         | 5.2.28                     | C1ODTCTRL—Channel 1 ODT Control                                      |

|   |         | 5.2.29                     | EPC0DRB0—ME Channel 0 DRAM Rank Boundary Address 0 145               |

|   |         | 5.2.30                     | EPC0DRB1—ME Channel 0 DRAM Rank Boundary Address 1 145               |

|   |         | 5.2.31                     | EPC0DRB2—ME Channel 0 DRAM Rank Boundary Address 2 146               |

|   |         | 5.2.32                     | EPC0DRB3—ME Channel 0 DRAM Rank Boundary Address 3 146               |

|   |         | 5.2.33                     | EPC0DRA01—ME Channel 0 DRAM Rank 0,1 Attribute                       |

|   |         | 5.2.34                     | EPC0DRA23—ME Channel 0 DRAM Rank 2,3 Attribute                       |

|   |         | 5.2.35                     | EPDCYCTRKWRTPRE—MED CYCTRK WRT PRE                                   |

|   |         | 5.2.36                     | EPDCYCTRKWRTACT—MED CYCTRK WRT ACT                                   |

|   |         | 5.2.37                     | EPDCYCTRKWRTWR—MED CYCTRK WRT WR                                     |

|   |         | 5.2.38                     | EPDCYCTRKWRTRD—MED CYCTRK WRT READ                                   |

|   |         | 5.2.39                     | EPDCKECONFIGREG—MED CKE Related Configuration Register 151           |

|   |         | 5.2.40                     | MEMEMSPACE—ME Memory Space configuration                             |

|   |         | 5.2.41                     | EPDREFCONFIG—ME DRAM Refresh Configuration                           |

|   |         | 5.2.42<br>5.2.43           | TSC2—Thermal Sensor Control 2                                        |

|   |         | 5.2.44                     | TSS—Thermal Sensor Status                                            |

|   |         | 5.2.45                     | TSTTP—Thermal Sensor Temperature Trip Point                          |

|   |         | 5.2.46                     | TCO—Thermal Calibration Offset                                       |

|   |         | 5.2.47                     | THERM1—Hardware Protection                                           |

|   |         | 5.2.48                     | TIS—Thermal Interrupt Status                                         |

|   |         | 5.2.49                     | TSMICMD—Thermal SMI Command                                          |

|   |         | 5.2.50                     | PMSTS—Power Management Status                                        |

|   | 5.3     |                            | Legisters                                                            |

|   | 5.5     | 5.3.1                      | EPESD—ME Element Self Description                                    |

|   |         | 5.3.2                      | EPLE1D—Controller Link Entry 1 Description                           |

|   |         | 5.3.3                      | EPLE1A—Controller Link Entry 1 Address                               |

|   |         | 5.3.4                      | EPLE2D—Controller Link Entry 2 Description                           |

|   |         | 5.3.5                      | EPLE2A—Controller Link Entry 2 Address                               |

| 6 | PCI Exp |                            | gisters (Device 1, Function 0) (Intel® 82Q965/82G965/82P965 Only)167 |

|   | 6.1     | PCI Expr                   | ess* Configuration Register Details (Device 1, Function 0) 170       |

|   |         | 6.1.1                      | VID1—Vendor Identification                                           |

|   |         | 6.1.2                      | DID1—Device Identification                                           |

|   |         | 6.1.3                      | PCICMD1—PCI Command                                                  |

|   |         | 6.1.4                      | PCISTS1—PCI Status                                                   |

|   |         | 6.1.5                      | RID1—Revision Identification                                         |

|   |         | 6.1.6                      | CC1—Class Code                                                       |

|   |         | 6.1.7                      | CL1—Cache Line Size                                                  |

|   |         | 6.1.8                      | HDR1—Header Type                                                     |

|   |         | 6.1.9                      | PBUSN1—Primary Bus Number                                            |

|   |         |                            |                                                                      |

|   |          | 6.1.10    | SBUSN1—Secondary Bus Number                          | 176 |

|---|----------|-----------|------------------------------------------------------|-----|

|   |          | 6.1.11    | SUBUSN1—Subordinate Bus Number                       | 176 |

|   |          | 6.1.12    | IOBASE1—I/O Base Address                             | 177 |

|   |          | 6.1.13    | IOLIMIT1—I/O Limit Address                           | 177 |

|   |          | 6.1.14    | SSTS1—Secondary Status                               | 178 |

|   |          | 6.1.15    | MBASE1—Memory Base Address                           |     |

|   |          | 6.1.16    | MLIMIT1—Memory Limit Address                         |     |

|   |          | 6.1.17    | PMBASE1—Prefetchable Memory Base Address             |     |

|   |          | 6.1.18    | PMLIMIT1—Prefetchable Memory Limit Address           | 182 |

|   |          | 6.1.19    | PMBASEU1—Prefetchable Memory Base Address            | 183 |

|   |          | 6.1.20    | PMLIMITU1—Prefetchable Memory Limit Address          |     |

|   |          | 6.1.21    | CAPPTR1—Capabilities Pointer                         |     |

|   |          | 6.1.22    | INTRLINE1—İnterrupt Line                             | 185 |

|   |          | 6.1.23    | INTRPIN1—Interrupt Pin                               |     |

|   |          | 6.1.24    | BCTRL1—Bridge Control                                |     |

|   |          | 6.1.25    | PM_CAPID1—Power Management Capabilities              | 188 |

|   |          | 6.1.26    | PM_CS1—Power Management Control/Status               |     |

|   |          | 6.1.27    | SS_CAPID—Subsystem ID and Vendor ID Capabilities     |     |

|   |          | 6.1.28    | SS—Subsystem ID and Subsystem Vendor ID              |     |

|   |          | 6.1.29    | MSI_CAPID—Message Signaled Interrupts Capability ID  |     |

|   |          | 6.1.30    | MC—Message Control                                   |     |

|   |          | 6.1.31    | MA—Message Address                                   |     |

|   |          | 6.1.32    | MD—Message Data                                      |     |

|   |          | 6.1.33    | PEG_CAPL—PCI Express* Capability List                |     |

|   |          | 6.1.34    | PEG_CAP—PCI Express* Capabilities                    |     |

|   |          | 6.1.35    | DCAP—Device Capabilities                             |     |

|   |          | 6.1.36    | DCTL—Device Control                                  |     |

|   |          | 6.1.37    | DSTS—Device Status                                   |     |

|   |          | 6.1.38    | LCAP—Link Capabilities                               |     |

|   |          | 6.1.39    | LCTL—Link Control                                    |     |

|   |          | 6.1.40    | LSTS—Link Status                                     |     |

|   |          | 6.1.41    | SLOTCAP—Slot Capabilities                            |     |

|   |          | 6.1.42    | SLOTCTL—Slot Control                                 |     |

|   |          | 6.1.43    | SLOTSTS—Slot Status                                  |     |

|   |          | 6.1.44    | RCTL—Root Control                                    |     |

|   |          | 6.1.45    | RSTS—Root Status                                     |     |

|   |          | 6.1.46    | PEGLC—PCI Express*-G Legacy Control                  |     |

|   |          | 6.1.47    | VCECH—Virtual Channel Enhanced Capability Header     |     |

|   |          | 6.1.48    | PVCCAP1—Port VC Capability Register 1                |     |

|   |          | 6.1.49    | PVCCAP2—Port VC Capability Register 2                |     |

|   |          | 6.1.50    | PVCCTL—Port VC Control                               |     |

|   |          | 6.1.51    | VCORCAP—VCO Resource Capability                      |     |

|   |          | 6.1.52    | VCORCTL—VCO Resource Control                         |     |

|   |          | 6.1.53    | VCORSTS—VCO Resource Status                          |     |

|   |          | 6.1.54    | RCLDECH—Root Complex Link Declaration Enhanced       |     |

|   |          | 6.1.55    | ESD—Element Self Description                         |     |

|   |          | 6.1.56    | LE1D—Link Entry 1 Description                        |     |

|   |          | 6.1.57    | LE1A—Link Entry 1 Address                            |     |

|   |          | 6.1.58    | PEGSSTS—PCI Express*-G Sequence Status               | 210 |

|   |          | 0.1.36    | PLG5515—PCI Express - G Sequence Status              | 219 |

| 7 | Direct M | 1emory I  | nterface (DMI) Registers                             | 221 |

|   | 7.1      | Direct Me | emory Interface (DMI) Configuration Register Details | 222 |

|   |          | 7.1.1     | DMIVCECH—DMI Virtual Channel Enhanced Capability     |     |

|   |          | 7.1.2     | DMIPVCCAP1—DMI Port VC Capability Register 1         |     |

|   |          | 7.1.3     | DMIPVCCAP2—DMI Port VC Capability Register 2         |     |

|   |          |           | , , ,                                                |     |

|   |     | 7.1.4    | DMIPVCCTL—DMI Port VC Control                                             | 224 |

|---|-----|----------|---------------------------------------------------------------------------|-----|

|   |     | 7.1.5    | DMIVCORCAP—DMI VCO Resource Capability                                    |     |

|   |     | 7.1.6    | DMIVCORCTLO—DMI VCO Resource Control                                      |     |

|   |     | 7.1.7    | DMIVCORSTS—DMI VC0 Resource Status                                        |     |

|   |     | 7.1.8    | DMIVC1RCAP—DMI VC1 Resource Capability                                    |     |

|   |     | 7.1.9    | DMIVC1RCTL1—DMI VC1 Resource Control                                      |     |

|   |     | 7.1.10   | DMIVC1RSTS—DMI VC1 Resource Status                                        |     |

|   |     | 7.1.11   | DMILCAP—DMI Link Capabilities                                             |     |

|   |     | 7.1.12   | DMILCTL—DMI Link Control                                                  |     |

|   |     | 7.1.12   | DMILSTS—DMI Link Status                                                   |     |

|   |     |          |                                                                           | 250 |

| 8 |     |          | nics Device Registers (Device 2) (Intel <sup>®</sup> 82Q965/82Q963/82G965 | 221 |

|   |     |          |                                                                           |     |

|   | 8.1 | IGD Conf | figuration Register Details (Device 2, Function 0)                        |     |

|   |     | 8.1.1    | VID2—Vendor Identification                                                | 233 |

|   |     | 8.1.2    | DID2—Device Identification                                                | 233 |

|   |     | 8.1.3    | PCICMD2—PCI Command                                                       | 234 |

|   |     | 8.1.4    | PCISTS2—PCI Status                                                        |     |

|   |     | 8.1.5    | RID2—Revision Identification                                              |     |

|   |     | 8.1.6    | CC—Class Code                                                             |     |

|   |     | 8.1.7    | CLS—Cache Line Size                                                       |     |

|   |     | 8.1.8    | MLT2—Master Latency Timer                                                 |     |

|   |     | 8.1.9    | HDR2—Header Type                                                          |     |

|   |     | 8.1.10   | GTTMMADR—Graphics Translation Table, Memory Mapped Range                  | 237 |

|   |     | 0.1.10   | Address                                                                   | 238 |

|   |     | 8.1.11   | GMADR—Graphics Memory Range Address                                       |     |

|   |     | 8.1.12   | IOBAR—IO Base Address                                                     |     |

|   |     | 8.1.13   | SVID2—Subsystem Vendor Identification                                     |     |

|   |     | 8.1.14   | SID2—Subsystem Identification                                             |     |

|   |     | 8.1.15   | ROMADR—Video BIOS ROM Base Address                                        |     |

|   |     |          |                                                                           |     |

|   |     | 8.1.16   | CAPPOINT—Capabilities Pointer                                             |     |

|   |     | 8.1.17   | INTRLINE—Interrupt Line                                                   |     |

|   |     | 8.1.18   | INTRPIN—Interrupt Pin                                                     |     |

|   |     | 8.1.19   | MINGNT—Minimum Grant                                                      |     |

|   |     | 8.1.20   | MAXLAT—Maximum Latency                                                    |     |

|   |     | 8.1.21   | MCAPPTR—Mirror of Device 0 Capabilities Pointer                           |     |

|   |     | 8.1.22   | CAPIDO—Mirror of Device 0 Capability Identifier                           |     |

|   |     | 8.1.23   | MGGC—Mirror of Device 0 GMCH Graphics Control Register                    |     |

|   |     | 8.1.24   | DEVEN—Mirror of Device 0 Device Enable                                    |     |

|   |     | 8.1.25   | SSRW—Software Scratch Read Write                                          |     |

|   |     | 8.1.26   | BSM—Base of Stolen Memory                                                 | 248 |

|   |     | 8.1.27   | HSRW—Hardware Scratch Read Write                                          |     |

|   |     | 8.1.28   | MSI_CAPID—Message Signaled Interrupts Capability ID                       | 249 |

|   |     | 8.1.29   | MC—Message Control                                                        | 249 |

|   |     | 8.1.30   | MA—Message Address                                                        |     |

|   |     | 8.1.31   | MD—Message Data                                                           |     |

|   |     | 8.1.32   | GDRST—Graphics Reset                                                      |     |

|   |     | 8.1.33   | PMCAPID—Power Management Capabilities ID                                  |     |

|   |     | 8.1.34   | PMCAP—Power Management Capabilities                                       |     |

|   |     | 8.1.35   | PMCS—Power Management Control/Status                                      |     |

|   |     | 8.1.36   | SWSMI—Software SMI                                                        |     |

|   | 0.2 |          |                                                                           |     |

|   | 8.2 |          | figuration Register Details (Device 2, Function 1)                        |     |

|   |     | 8.2.1    | VID2—Vendor Identification                                                |     |

|   |     | 8.2.2    | DID2—Device Identification                                                |     |

|   |     | 823      | PCICMD2—PCI Command                                                       | 257 |

|   |        | 8.2.4       | PCISTS2—PCI Status                                                                                     |            |

|---|--------|-------------|--------------------------------------------------------------------------------------------------------|------------|

|   |        | 8.2.5       | RID2—Revision Identification                                                                           | 259        |

|   |        | 8.2.6       | CC—Class Code Register                                                                                 | 259        |

|   |        | 8.2.7       | CLS—Cache Line Size                                                                                    | 260        |

|   |        | 8.2.8       | MLT2—Master Latency Timer                                                                              | 260        |

|   |        | 8.2.9       | HDR2—Header Type                                                                                       |            |

|   |        | 8.2.10      | MMADR—Memory Mapped Range Address                                                                      |            |

|   |        | 8.2.11      | SVID2—Subsystem Vendor Identification                                                                  |            |

|   |        | 8.2.12      | SID2—Subsystem Identification                                                                          |            |

|   |        | 8.2.13      | ROMADR—Video BIOS ROM Base Address                                                                     |            |

|   |        | 8.2.14      | CAPPOINT—Capabilities Pointer                                                                          |            |

|   |        | 8.2.15      | MINGNT—Minimum Grant                                                                                   |            |

|   |        | 8.2.16      |                                                                                                        |            |

|   |        | 8.2.17      | MAXLAT—Maximum Latency  MCAPPTR—Mirror of Device 0 Capabilities Pointer                                |            |

|   |        | 8.2.18      | · · · · · · · · · · · · · · · · · · ·                                                                  |            |

|   |        | -           | CAPIDO—Capability Identifier                                                                           |            |

|   |        | 8.2.19      | MGGC—Mirror of Device 0 GMCH Graphics Control Register                                                 |            |

|   |        | 8.2.20      | DEVEN—Device Enable                                                                                    |            |

|   |        | 8.2.21      | SSRW—Mirror Function 0 Software Scratch Read/Write                                                     |            |

|   |        | 8.2.22      | BSM—Mirror of Function 0 Base of Stolen Memory                                                         |            |

|   |        | 8.2.23      | HSRW—Mirror of Device 2, Function 0 Hardware Scratch Read-Wr                                           |            |

|   |        | 8.2.24      | PMCAPID—Mirror Function 0 Power Management Capabilities ID                                             |            |

|   |        | 8.2.25      | PMCAP—Mirror Function 0 Power Management Capabilities                                                  |            |

|   |        | 8.2.26      | PMCS—Power Management Control/Status                                                                   |            |

|   |        | 8.2.27      | SWSMI—Mirror of Function 0 Software SMI                                                                | 271        |

| 9 | Manage | eability Er | ngine (ME) Subsystem Registers (Device 3, Functions 0,1,2)                                             | 273        |

|   | 9.1    | Host Eml    | bedded Controller Interface (HECI1) Configuration Register Details                                     |            |

|   |        |             | 3, Function 0)                                                                                         |            |

|   |        | 9.1.1       | ID—Identifiers                                                                                         |            |

|   |        | 9.1.2       | CMD—Command                                                                                            |            |

|   |        | 9.1.3       | STS—Device Status                                                                                      |            |

|   |        | 9.1.4       | RID—Revision ID                                                                                        |            |

|   |        | 9.1.5       | CC—Class Code                                                                                          |            |

|   |        | 9.1.6       | CLS—Cache Line Size                                                                                    |            |

|   |        | 9.1.7       | MLT—Master Latency Timer                                                                               |            |

|   |        | 9.1.8       | HTYPE—Header Type                                                                                      |            |

|   |        | 9.1.9       | HECI_MBAR—HECI MMIO Base Address                                                                       |            |

|   |        | 9.1.10      | SS—Sub System Identifiers                                                                              |            |

|   |        | 9.1.11      | CAP—Capabilities Pointer                                                                               |            |

|   |        | 9.1.12      | INTR—Interrupt Information                                                                             |            |

|   |        | 9.1.13      | MGNT—Minimum Grant                                                                                     |            |

|   |        | 9.1.14      | MLAT—Maximum Latency                                                                                   |            |

|   |        | 9.1.15      | HFS—Host Firmware Status                                                                               |            |

|   |        | 9.1.16      | PID—PCI Power Management Capability ID                                                                 |            |

|   |        | 9.1.10      |                                                                                                        |            |

|   |        | _           | PC—PCI Power Management Capabilities                                                                   |            |

|   |        | 9.1.18      | PMCS—PCI Power Management Control And Status                                                           |            |

|   |        | 9.1.19      | MID—Message Signaled Interrupt Identifiers                                                             |            |

|   |        | 9.1.20      | MC—Message Signaled Interrupt Message Control                                                          |            |

|   |        | 9.1.21      | MA—Message Signaled Interrupt Message Address                                                          |            |

|   |        | 9.1.22      | MD—Message Signaled Interrupt Message Data                                                             |            |

|   |        | 9.1.23      | HIDM—HECI Interrupt Delivery Mode                                                                      |            |

|   |        |             |                                                                                                        | h h        |

|   | 9.2    |             | onfiguration Register Details (Device 3, Function 1) ) (Intel $^{	ext{	iny 8}}$ 82Q9 $^{	ext{	iny 1}}$ |            |

|   | 9.2    | GMCH Or     | nly)                                                                                                   | 287        |

|   | 9.2    |             |                                                                                                        | 287<br>288 |

|     | 9.2.3            | STS—Device Status                                                    | 290   |

|-----|------------------|----------------------------------------------------------------------|-------|

|     | 9.2.4            | RID—Revision ID                                                      | 291   |

|     | 9.2.5            | CC—Class Code                                                        | 291   |

|     | 9.2.6            | CLS—Cache Line Size                                                  | 291   |

|     | 9.2.7            | MLT—Master Latency Timer                                             |       |

|     | 9.2.8            | HTYPE—Header Type                                                    |       |

|     | 9.2.9            | BIST—Built In Self Test                                              |       |

|     | 9.2.10           | HECI MBAR—HECI MMIO Base Address                                     |       |

|     | 9.2.11           | SS—Sub System Identifiers                                            |       |

|     | 9.2.12           | CAP—Capabilities Pointer                                             |       |

|     | 9.2.13           | INTR—Interrupt Information                                           |       |

|     | 9.2.14           | MGNT—Minimum Grant                                                   |       |

|     | 9.2.15           | MLAT—Maximum Latency                                                 |       |

|     | 9.2.16           | HFS—Host Firmware Status                                             |       |

|     | 9.2.17           | PID—PCI Power Management Capability ID                               |       |

|     | 9.2.17           | PC—PCI Power Management Capabilities                                 |       |

|     | 9.2.18           | PMCS—PCI Power Management Control and Status                         | 290   |

|     | 9.2.19           | MID—Message Signaled Interrupt Identifiers                           | 200   |

|     |                  | MC—Message Signaled Interrupt Message Control                        | 200   |

|     | 9.2.21           |                                                                      |       |

|     | 9.2.22<br>9.2.23 | MA—Message Signaled Interrupt Message Address (Optional)             |       |

|     |                  | MUA—Message Signaled Interrupt Upper Address (Optional)              |       |

|     | 9.2.24<br>9.2.25 | MD—Message Signaled Interrupt Message Data                           |       |

| 0.0 |                  | HIDM—HECI Interrupt Delivery Mode                                    | 201   |

| 9.3 |                  | Configuration Register Details (Device 3, Function 2) (Intel® 82Q9   |       |

|     |                  | nly)                                                                 |       |

|     | 9.3.1            | ID—Identification                                                    |       |

|     | 9.3.2            | CMD—Command Register                                                 |       |

|     | 9.3.3            | STS—Device Status                                                    |       |

|     | 9.3.4            | RID—Revision ID                                                      |       |

|     | 9.3.5            | CC—Class Codes                                                       |       |

|     | 9.3.6            | CLS—Cache Line Size                                                  |       |

|     | 9.3.7            | MLT—Master Latency Timer                                             |       |

|     | 9.3.8            | HTYPE—Header Type                                                    |       |

|     | 9.3.9            | PCMDBA—Primary Command Block IO Bar                                  |       |

|     | 9.3.10           | PCTLBA—Primary Control Block Base Address                            |       |

|     | 9.3.11           | SCMDBA—Secondary Command Block Base Address                          |       |

|     | 9.3.12           | SCTLBA—Secondary Control Block base Address                          | 309   |

|     | 9.3.13           | LBAR—Legacy Bus Master Base Address                                  | 309   |

|     | 9.3.14           | SS—Sub System Identifiers                                            | 310   |

|     | 9.3.15           | EROM—Expansion ROM Base Address                                      | 310   |

|     | 9.3.16           | CAP—Capabilities Pointer                                             |       |

|     | 9.3.17           | INTR—Interrupt Information                                           |       |

|     | 9.3.18           | MGNT—Minimum Grant                                                   |       |

|     | 9.3.19           | MLAT—Maximum Latency                                                 |       |

|     | 9.3.20           | PID—PCI Power Management Capability ID                               | 312   |

|     | 9.3.21           | PC—PCI Power Management Capabilities                                 |       |

|     | 9.3.22           | PMCS—PCI Power Management Control and Status                         |       |

|     | 9.3.23           | MID—Message Signaled Interrupt Capability ID                         |       |

|     | 9.3.24           | MC—Message Signaled Interrupt Message Control                        |       |

|     | 9.3.25           | MA—Message Signaled Interrupt Message Address                        |       |

|     | 9.3.26           | MAU—Message Signaled Interrupt Message Upper Address                 |       |

|     | 9.3.27           | MD—Message Signaled Interrupt Message Data                           |       |

| 9.4 |                  | irection Configuration Register Details (Device 3, Function 3) (Inte |       |

| J.7 |                  | GMCH Only)Giration Register Details (Device 3, 1 unction 3) (Inte    |       |

|     | -                | ID—Identification                                                    |       |

|     | 9.4.1            | 1D—10eHullCation                                                     | . 515 |

|    |        | 9.4.2     | CMD—Command Register                                            |           |

|----|--------|-----------|-----------------------------------------------------------------|-----------|

|    |        | 9.4.3     | STS—Device Status                                               | . 320     |

|    |        | 9.4.4     | RID—Revision ID                                                 | . 321     |

|    |        | 9.4.5     | CC—Class Codes                                                  | . 322     |

|    |        | 9.4.6     | CLS—Cache Line Size                                             |           |

|    |        | 9.4.7     | MLT—Master Latency Timer                                        | . 322     |

|    |        | 9.4.8     | HTYPE—Header Type                                               | . 323     |

|    |        | 9.4.9     | KTIBA—KT IO Block Base Address                                  | . 323     |

|    |        | 9.4.10    | KTMBA—KT Memory Block Base Address                              | . 324     |

|    |        | 9.4.11    | SS—Sub System Identifiers                                       | . 324     |

|    |        | 9.4.12    | EROM—Expansion ROM Base Address                                 | . 325     |

|    |        | 9.4.13    | CAP—Capabilities Pointer                                        | . 325     |

|    |        | 9.4.14    | INTR—Interrupt Information                                      | . 326     |

|    |        | 9.4.15    | MGNT—Minimum Grant                                              | . 326     |

|    |        | 9.4.16    | MLAT—Maximum Latency                                            | . 327     |

|    |        | 9.4.17    | PID—PCI Power Management Capability ID                          |           |

|    |        | 9.4.18    | PC—PCI Power Management Capabilities                            | . 328     |

|    |        | 9.4.19    | PMCS—PCI Power Management Control and Status                    |           |

|    |        | 9.4.20    | MID—Message Signaled Interrupt Capability ID                    | . 330     |

|    |        | 9.4.21    | MC—Message Signaled Interrupt Message Control                   | . 330     |

|    |        | 9.4.22    | MA—Message Signaled Interrupt Message Address                   |           |

|    |        | 9.4.23    | MAU—Message Signaled Interrupt Message Upper Address            | . 331     |

|    |        | 9.4.24    | MD—Message Signaled Interrupt Message Data                      | . 332     |

| 10 | Eunsti | anal Daca | ription                                                         | 222       |

| 10 |        |           | ·                                                               |           |

|    | 10.1   |           | erface                                                          |           |

|    |        | 10.1.1    | FSB IOQ Depth                                                   |           |

|    |        | 10.1.2    | FSB OOQ Depth                                                   |           |

|    |        | 10.1.3    | FSB GTL+ Termination                                            |           |

|    |        | 10.1.4    | FSB Dynamic Bus Inversion                                       |           |

|    | 10.2   | System    | Memory Controller                                               | . 335     |

|    |        | 10.2.1    | DRAM Technologies and Organization                              | . 337     |

|    |        | 10.2.2    | Memory Detection and Initialization                             |           |

|    |        | 10.2.3    | DRAM Clock Generation                                           |           |

|    |        | 10.2.4    | Suspend to RAM and Resume                                       |           |

|    |        | 10.2.5    | DDR2 On-Die Termination                                         |           |

|    | 10.3   | PCI Exp   | ress* (Intel® 82Q965, 82G965, 82P965 (G)MCH)                    |           |

|    |        | 10.3.1    | Transaction Layer                                               |           |

|    |        | 10.3.2    | Data Link Layer                                                 |           |

|    |        | 10.3.3    | Physical Layer                                                  |           |

|    | 10.4   |           | erial Digital Video Output (SDVO) (Intel® 82Q965, 82Q963, 82G96 |           |

|    | 1011   | GMCH C    | Only)                                                           | .344      |

|    |        | 10.4.1    | Intel <sup>®</sup> SDVO Capabilities                            |           |

|    |        | 10.4.2    | Intel® SDVO Modes                                               | . 345     |

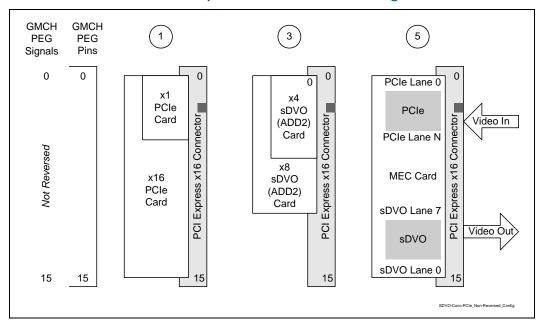

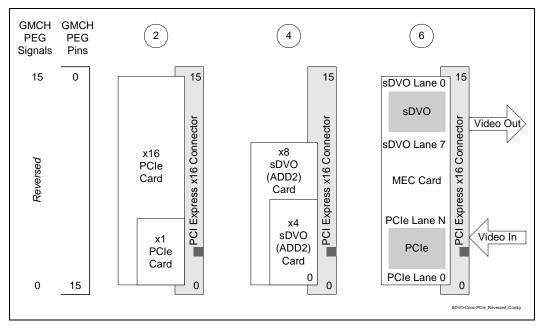

|    |        | 10.4.2    | PCI Express* and Internal Graphics Simultaneous Operation (Inte | ופ<br>®ור |

|    |        | 10.7.5    | 82Q965, 82G965 Only)                                            |           |

|    | 10.5   | Integrat  | red Graphics Device (IGD) (Intel® 82Q965, 82Q963, 82G965 GMCH   |           |

|    | 10.5   |           |                                                                 |           |

|    |        | 10.5.1    | Overview                                                        |           |

|    | 10.6   |           | Interfaces                                                      |           |

|    | _0.0   | 10.6.1    | Analog Display Port Characteristics                             |           |

|    |        | 10.6.2    | Digital Display Interface                                       |           |

|    |        | 10.6.3    | Multiple Display Configurations                                 | . 355     |

|    | 10.7   |           | lanagement                                                      |           |

|    | 10.,   |           | ·~··~g-····c···c                                                | . 555     |

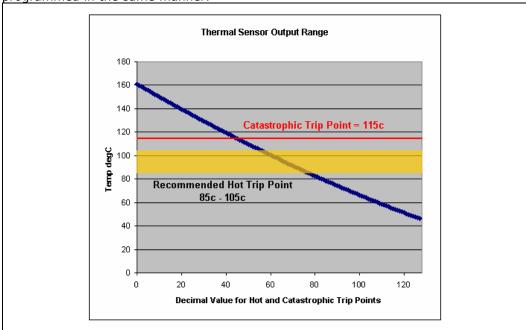

|    | 10.8    | Thermal    | Sensor                                                 | 356 |

|----|---------|------------|--------------------------------------------------------|-----|

|    |         | 10.8.1     | PCI Device 0, Function 0                               |     |

|    |         | 10.8.2     | MCHBAR Thermal Sensor Registers                        |     |

|    |         | 10.8.3     | Programming Sequence                                   |     |

|    | 10.0    | 10.8.4     | Trip Point Temperature Programming                     |     |

|    | 10.9    | Clocking   |                                                        | 359 |

| 11 | Electri | cal Charac | teristics                                              | 361 |

|    | 11.1    | Absolute   | Minimum and Maximum Ratings                            | 361 |

|    |         | 11.1.1     |                                                        |     |

|    | 11.2    | Signal G   | roups                                                  | 364 |

|    | 11.3    | Buffer Si  | upply and DC Characteristics                           | 367 |

|    |         | 11.3.1     | I/O Buffer Supply Voltages                             | 367 |

|    |         | 11.3.2     | General DC Characteristics                             |     |

|    |         | 11.3.3     | R, G, B / CRT DAC Display DC Characteristics (Intel® 8 |     |

|    |         |            | 82Q963, 82G965 GMCH Only)                              | 372 |

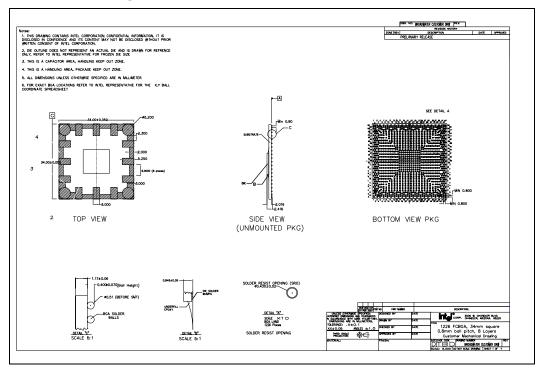

| 12 | Ballou  | t and Pack | age Information                                        | 373 |

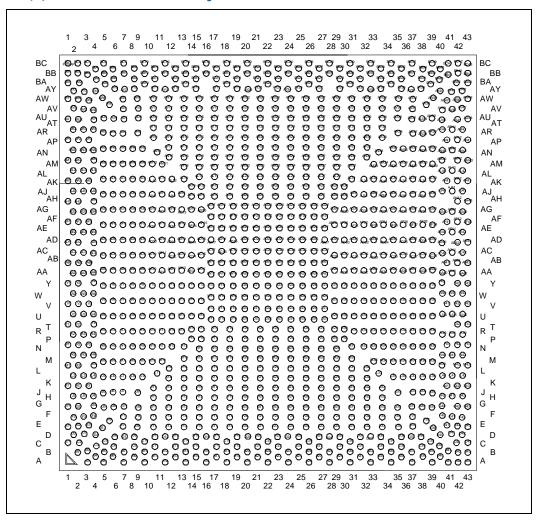

|    | 12.1    | Ballout    |                                                        | 373 |

|    | 12.2    | Package    | Dimensions                                             | 389 |

| 13 | Testal  | oility     |                                                        | 391 |

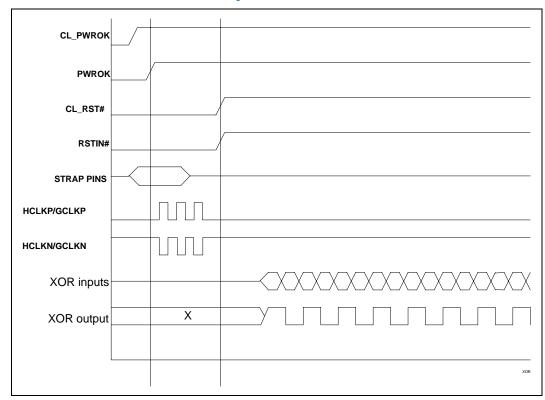

|    | 13.1    | XOR Tes    | t Mode Initialization                                  | 391 |

|    | 13.2    |            | in Definition                                          |     |

|    | 13.3    |            | ins                                                    |     |

|    | 13.3    |            | cluded from XOR Mode(s)                                |     |

|    | 13.4    | PADS EX    | ciuded itotti AOK Mode(S)                              | 402 |

### **Figures**

**Tables**

| Figure 1-1. Intel® Q965/G965 Express Chipset System Block Diagram Example                                       |

|-----------------------------------------------------------------------------------------------------------------|

| Figure 12-3. (G)MCH Ballout Diagram (Top View Right – Columns 14–0)                                             |

| Figure 12-4. (G)MCH Package Dimensions                                                                          |

| Figure 12-5. (G)MCH Non-Grid Ball Array                                                                         |

|                                                                                                                 |

|                                                                                                                 |

| Table 2-1. Signal Terminology                                                                                   |

| Table 2-2. SDVO/PCI Express* Signal Mapping (Intel® 82Q965 and 82G965 Only)47                                   |

| Table 3-1. Expansion Area Memory Segments                                                                       |

| Table 3-2. Extended System BIOS Area Memory Segments                                                            |

| Table 3-4. Specifics of Legacy Interrupt Routing                                                                |

| Table 3-5. Pre-allocated Memory Example for 64 MB DRAM, 1 MB VGA, and 1 MB TSEG58                               |

| Table 3-6. Pre-Allocated Memory Example for 64-MB DRAM, 1-MB VGA and 1-MB TSEG65                                |

| Table 3-7. SMM Space Table                                                                                      |

| Table 3-8. SMM Control Table                                                                                    |

| Table 5-1. DRAM Controller Register Address Map (Device 0, Function 0)83 Table 5-2. MCHBAR Register Address Map |

| Table 5-2. MCHBAR Register Address Map                                                                          |

| Table 5-4. MEBAR Register Address Map                                                                           |

| Table 6-1. PCI Express* Register Address Map (Device 1, Function 0)                                             |

| Table 7-1. DMI Register Address Map                                                                             |

| Table 8-1. Integrated Graphics Device Register Address Map (Device 2, Function 0)231                            |

| Table 8-2. Integrated Graphics Device Register Address Map (Device 2, Function 1)255                            |

| Table 9-1. HECI1 Register Address Map (Device 3, Function 0)                                                    |

| Table 9-2. HECI2 Register Address Map (Device 3, Function 1)                                                    |

| Table 9-3. PT IDER Register Address Map (Device 3, Function 2)                                                  |

| Table 9-4. (KT) Redirection Register Address Map (Device 3, Function3)                                          |

| Table 10-1. Sample System Memory Organization with Interleaved Channels           |     |

|-----------------------------------------------------------------------------------|-----|

| Table 10-2. Sample System Memory Organization with Asymmetric Channels            | 335 |

| Table 10-3. DDR2 DIMM Supported Configurations                                    | 339 |

| Table 10-4. DRAM Address Translation (Single Channel/Dual Asymmetric Mode)        |     |

| Table 10-5. DRAM Address Translation (Dual Channel Symmetric Mode)                |     |

| Table 10-6. Concurrent SDVO / PCI Express* Configuration Strap Controls           | 346 |

| Table 10-7. Display Port Characteristics                                          |     |

| Table 10-8. Analog Port Characteristics                                           |     |

| Table 11-1. Absolute Minimum and Maximum Ratings                                  |     |

| Table 11-2. Current Consumption in S0                                             |     |

| Table 11-3. Signal Groups                                                         |     |

| Table 11-4. I/O Buffer Supply Voltage                                             |     |

| Table 11-5. DC Characteristics                                                    |     |

| Table 11-6. R, G, B / CRT DAC Display DC Characteristics: Functional Operating Ra |     |

| $(VCCA\_DAC = 3.3 V \pm 5\%)$                                                     |     |

| Table 12-1. (G)MCH Ballout Sorted by Signal Name                                  |     |

| Table 13-1. XOR Chain 14 functionality                                            |     |

| Table 13-2. XOR Chain Outputs                                                     |     |

| Table 13-3. XOR Chain 0                                                           |     |

| Table 13-4. XOR Chain 1                                                           |     |

| Table 13-5. XOR Chain 2                                                           |     |

| Table 13-6. XOR Chain 3                                                           |     |

| Table 13-7. XOR Chain 4                                                           |     |

| Table 13-8. XOR Chain 5                                                           |     |

| Table 13-9. XOR Chain 6                                                           |     |

| Table 13-10. XOR Chain 7                                                          |     |

| Table 13-11. XOR Chain 8                                                          |     |

| Table 13-12. XOR Chain 9                                                          |     |

| Table 13-13. XOR Chain 10                                                         |     |

| Table 13-14. XOR Chain 11                                                         |     |

| Table 13-15. XOR Chain 12                                                         |     |

| Table 13-16. XOR Chain 13                                                         |     |

| Table 13-17. XOR Chain 14                                                         |     |

| Table 13-18. XOR Pad Exclusion List                                               | 402 |

## **Revision History**

| Revision | Description                                       | Date      |

|----------|---------------------------------------------------|-----------|

| -001     | Initial Release                                   | June 2006 |

| -002     | Added 82Q965, 82G965, and 82Q963 GMCH components. | July 2006 |

§

# Intel® 82Q965, 82Q963, 82G965, 82P965 (G)MCH Features

- Processor/Host Interface (FSB)

- —Supports a single Intel® Core™2 Duo desktop processor, Intel® Pentium® 4 processor, or Intel® Pentium® D processor.

- Supports Pentium 4 processor / Pentium D processor subset of the Extended Mode Scaleable Bus Protocol.

- —Supports Pentium 4 processor / Pentium D processor FSB interrupt delivery

- -533/800/1066 MT/s (133/200/266 MHz) FSB

- —Hyper-Threading Technology (HT Technology)

- —FSB Dynamic Bus Inversion (DBI)

- -36-bit host bus addressing

- -12-deep In-Order Queue

- -1-deep Defer Queue

- —GTL+ bus driver with integrated GTL termination resistors

- —Supports cache Line Size of 64 bytes

- System Memory Interface

- One or two channels (each channel consisting of 64 data lines)

- —Channels are asymmetric, interleaved

- —DDR2-800/667/533 frequencies

- -Unbuffered DIMMs only

- —Supports 256-Mb, 512-Mb, and 1-Gb technologies for x8 and x16 devices

- —Supports four banks for all DDR2 devices up to 512-Mbit density. Supports eight banks for 1-Gbit DDR2 devices

- —8 GB maximum memory

- Direct Media Interface (DMI)

- —Chip-to-chip connection interface to Intel ICH8

- —2 GB/s point-to-point DMI to ICH8 (1 GB/s each direction)

- —100 MHz reference clock (shared with PCI Express graphics attach)

- —32-bit downstream addressing

- —Messaging and Error Handling

- PCI Express\* Interface (82Q965, 82G965, 82P965 (G)MCH only)

- -One x16 PCI Express port

- —Compatible with the PCI Express Base Specification, Revision 1.1a

- —Raw bit rate on data pins of 2.5 Gb/s resulting in a real bandwidth per pair of 250 MB/s

- Intel<sup>®</sup> Active Management Technology (82G965 GMCH only)

- —Asset Management

- —OOB diagnostics

- —Network protection with NOC filters and agent presence

- —Integrated hardware/software platform solution

- Integrated Graphics Device (82Q965, 82Q963, 82G965 GMCH only)

- —Core frequency of 400 MHz

- —1.6 GP/s pixel rate

- —High-Quality 3D Setup and Render Engine

- —High-Quality Texture Engine

- —3D Graphics Rendering Enhancements

- -2D Graphics

- -Video Overlay

- —Multiple Overlay Functionality

- Analog Display (82Q965, 82Q963, 82G965 GMCH only)

- —400 MHz Integrated 24-bit RAMDAC

- —Up to 2048x1536 @ 75 Hz refresh

- —Hardware Color Cursor Support

- —DDC2B Compliant Interface

- Digital Display (82Q965, 82Q963, 82G965 GMCH only)

- —SDVO ports in either single/single-combined or dual operation modes supported

- -270 MHz dot clock on each 12-bit interface

- —Flat panels up to 2048x1536 @ 60 Hz or digital CRT/HDTV at 1920x1080 @ 85Hz

- —Dual independent display options with digital display

- Multiplexed digital display channels (supported with ADD2 Card).

- —Supports TMDS transmitters or TV-Out encoders

- —ADD2/ADD2+ card uses PCI Express graphics x16 connector

- —Two channels multiplexed with PCI Express\* Graphics port

- —Supports Hot-Plug and Display

- —Supports TMDS transmitters or TV-out encoders

- Thermal Sensor

- —Catastrophic Trip Point support

- —Hot Trip Point support for SMI generation

- Power Management

- —PC99 suspend to DRAM support ("STR", mapped to ACPI state S3)

- ACPI Revision 1.0 compatible power management

- —Supports processor states: C0 and C1

- —Supports System states: S0, S1D, S3, S4, and S5

- —Supports processor Thermal Management 2 (TM2)

- Package

- $-34 \text{ mm} \times 34 \text{ mm}$ . The 1226 balls are located in a non-grid pattern

§

### 1 Introduction

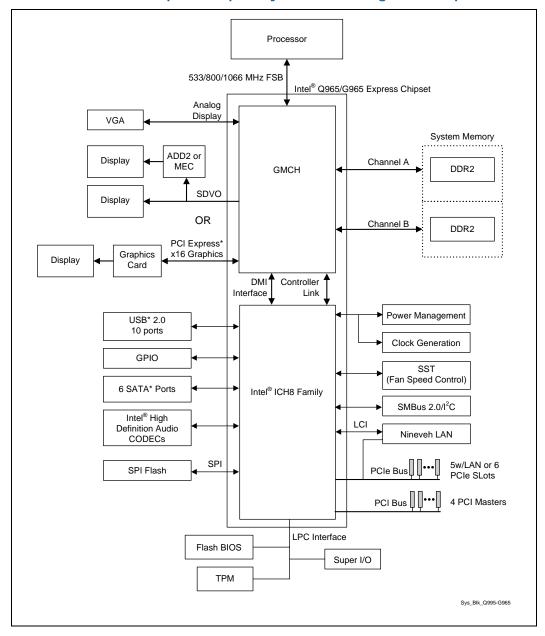

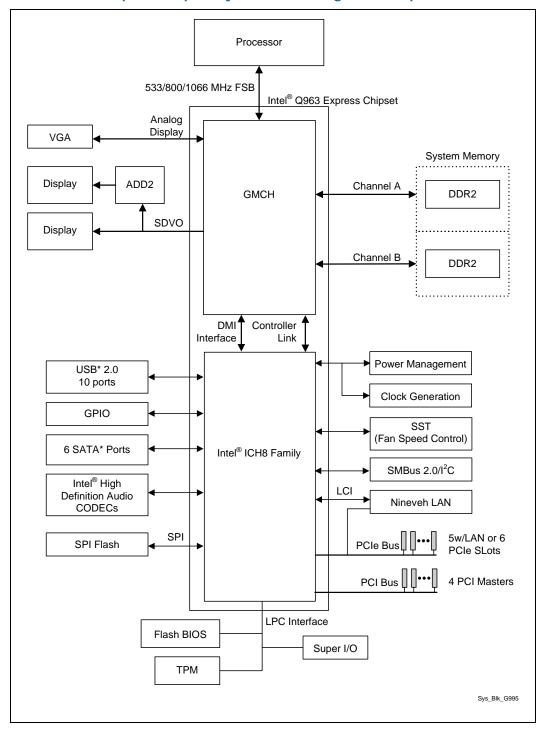

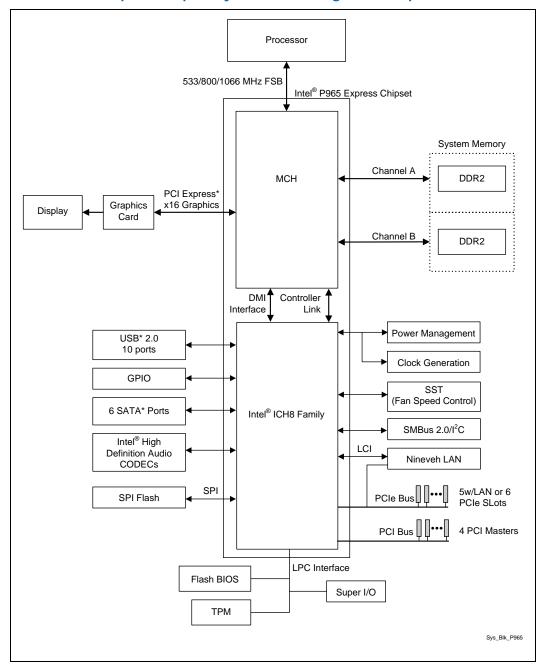

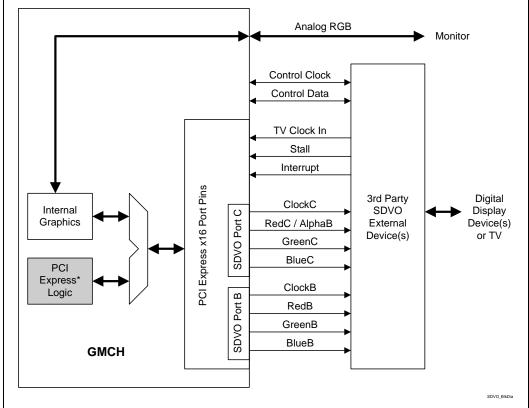

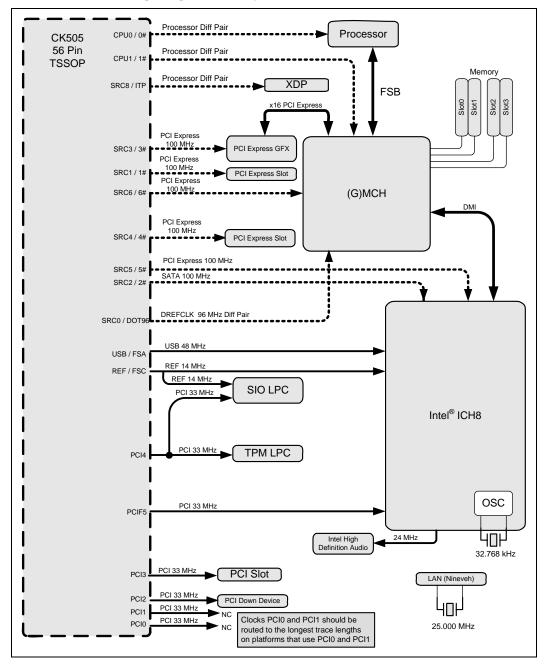

The Intel® Q965/Q963/G965G/P965 Express chipsets are designed for use with the Intel® Core™2 Duo desktop processor, Intel® Pentium® D processor, and Intel® Pentium® 4 processor based platforms. Each chipset contains two components: GMCH (or MCH) for the host bridge and I/O Controller Hub 8 (ICH8) for the I/O subsystem. The 82Q965 GMCH is part of the Q965 Express chipset, 82Q963 GMCH is part of the Q963 Express chipset, 82G965 GMCH is part of the G965 Express chipset, and 82P965 MCH is part of the P965 Express chipset. The ICH8 is the eighth generation I/O Controller Hub and provides a multitude of I/O related functions. The following figures show example system block diagrams for the Q965, Q963, G965, and P965 Express chipsets.

This document is the datasheet for the Intel® 82Q965 Graphics and Memory Controller Hub (GMCH), Intel® 82Q963 Graphics and Memory Controller Hub (GMCH), Intel® 82G965 Graphics and Memory Controller Hub (MCH), and Intel® 82P965 Memory Controller Hub (MCH). Topics covered include; signal description, system memory map, PCI register description, a description of the (G)MCH interfaces and major functional units, electrical characteristics, ballout definitions, and package characteristics.

**Note:** Unless otherwise specified, the information in this document applies to the Intel<sup>®</sup> 82Q965 Graphics and Memory Controller Hub (GMCH), Intel<sup>®</sup> 82Q963 Graphics and Memory Controller Hub (GMCH), Intel<sup>®</sup> 82G965 Graphics and Memory Controller Hub (GMCH), and Intel<sup>®</sup> 82P965 Memory Controller Hub (MCH).

Note: The term (G)MCH refers to the 82Q965/82Q963/82G965 GMCH and 82P965 MCH.

**Note:** Unless otherwise specified, ICH8 refers to the Intel<sup>®</sup> 82801HB ICH8 and 82801HR ICH8R I/O Controller Hub 8 components.

The primary differences between the 82Q965 GMCH, 82Q963 GMCH, 82G965 GMCH, and 82P965 MCH are:

| Capability                                                                  | Intel® 82Q965          | Intel® 82Q963    | Intel® 82G965          | Intel® 82P965          |

|-----------------------------------------------------------------------------|------------------------|------------------|------------------------|------------------------|

| Memory Speed                                                                | DDR2-<br>800/667/533   | DDR2-<br>667/533 | DDR2-<br>800/667/533   | DDR2-<br>800/667/533   |

| Integrated<br>Graphics Device                                               | Yes                    | Yes              | Yes                    | No                     |

| Discrete Graphics                                                           | PCI Express<br>x16     | None             | PCI Express<br>x16     | PCI Express<br>x16     |

| PCI Express<br>Interface                                                    | Yes<br>(1) x16, (6) x1 | No<br>(6) x1     | Yes<br>(1) x16, (6) x1 | Yes<br>(1) x16, (6) x1 |

| Advanced Media<br>Capabilities                                              | No                     | No               | Yes                    | No                     |

| SDVO Expansion                                                              | MEC / ADD2             | Add2 only        | MEC / ADD2             | _                      |

| Dual Independent<br>Display                                                 | Yes                    | No               | Yes                    | _                      |

| Intel <sup>®</sup> Active<br>Management<br>Technology<br>(AMT) <sup>2</sup> | Yes <sup>1</sup>       | No               | No                     | No                     |

| Alerting Standard<br>Format (ASF)                                           | Yes <sup>1</sup>       | Yes              | No                     | No                     |

#### NOTE:

- 1. For the 82Q965, only one manageability solution can be supported, AMT or ASF.

- 2. Intel® Active Management Technology requires the platform to have an Intel® AMT-enabled chipset, network hardware and software, connection with a power source and an active LAN port.

Figure 1-1. Intel® Q965/G965 Express Chipset System Block Diagram Example

Figure 1-2. Intel<sup>®</sup> Q963 Express Chipset System Block Diagram Example

Figure 1-3. Intel® P965 Express Chipset System Block Diagram Example

### 1.1 Terminology

| Term                                | Decemention                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                 |

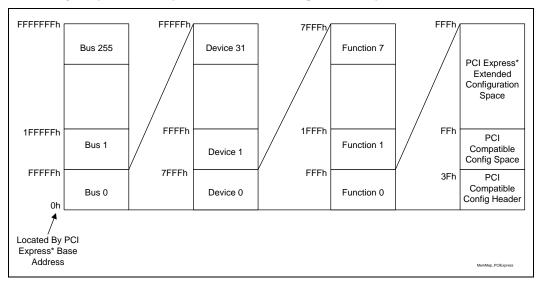

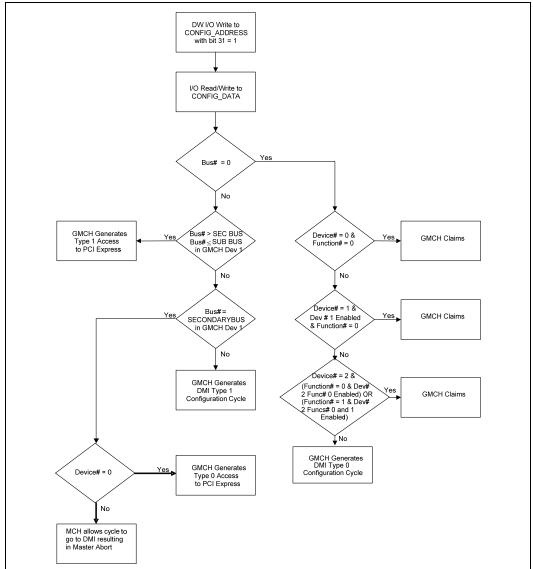

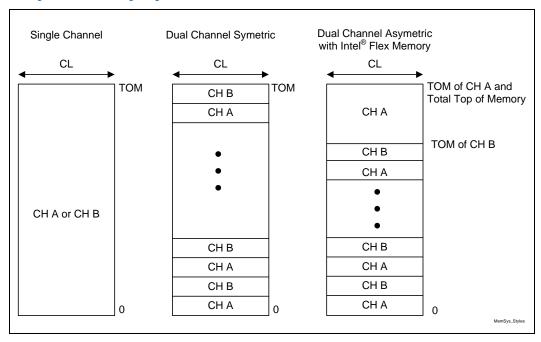

| ADD Card                            | Advanced Digital Display Card. Provides digital display options for an Intel Graphics Controller that supports ADD cards (have DVOs multiplexed with AGP interface). Keyed like an AGP 4x card and plugs into an AGP connector. Will <b>not</b> work with an Intel Graphics Controller that implements Intel <sup>®</sup> SDVO.                                                                                                             |